# Arquitecturas de DSP TMS320F28xxx y aplicaciones

F.I. UNAM. Larry Escobar

| • |      |                   |      |     |

|---|------|-------------------|------|-----|

| т | ndic |                   |      | 1   |

|   | กสเด | $\alpha \alpha c$ | ana. | ral |

|   |      |                   |      |     |

# Índice general

| 1. | Intr | roducción                                                                 | 1               |

|----|------|---------------------------------------------------------------------------|-----------------|

| 2. | Car  | acterísticas generales de la familia F28xx                                | 5               |

| 3. |      | uitectura de la familia F28xx                                             | 11              |

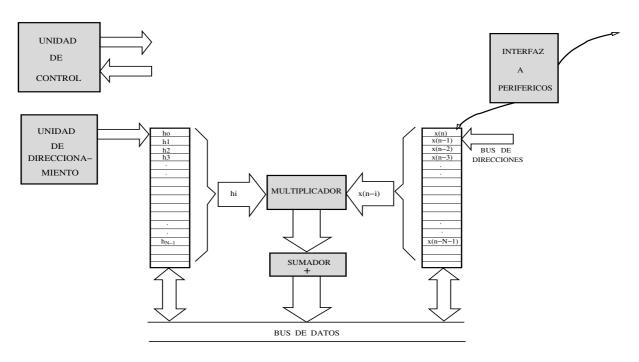

|    | 3.1. | La convolución y el núcleo de un DSP                                      | 11              |

|    | 3.2. | Arquitectura general de los DSP C28x                                      | 13              |

|    | 3.3. | Buses y registros del CPU                                                 | 13              |

|    |      | 3.3.1. Descripción de registros                                           | 16              |

|    | 3.4. | Unidad central de proceso                                                 | 20              |

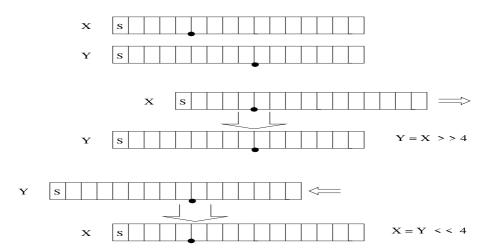

|    |      | 3.4.1. Registros de corrimiento                                           | 20              |

|    |      | 3.4.2. Unidad aritmético lógica (ALU)                                     | 22              |

|    |      | 3.4.3. Multiplicador                                                      | $2\overline{2}$ |

|    | 3.5. | Pipeline                                                                  | 23              |

| 4. | Mer  | moria y modos de direccionamiento                                         | 27              |

|    | 4.1. | Mapa de memoria                                                           | 27              |

|    |      | 4.1.1. Memoria flash y SARAM                                              | 29              |

|    |      | 4.1.2. Vectores de interrupción                                           | 30              |

|    |      | 4.1.3. Buses internos                                                     | 30              |

|    |      | 4.1.4. Seguridad                                                          | 31              |

|    |      | 4.1.5. Sintaxis de instrucciones                                          | 31              |

|    | 4.2. | Modos de direccionamiento                                                 | 35              |

|    |      | 4.2.1. Direccionamiento inmediato                                         | 35              |

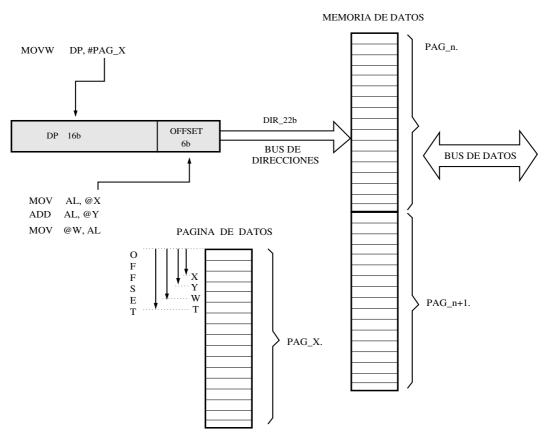

|    |      | 4.2.2. Direccionamiento directo                                           | 36              |

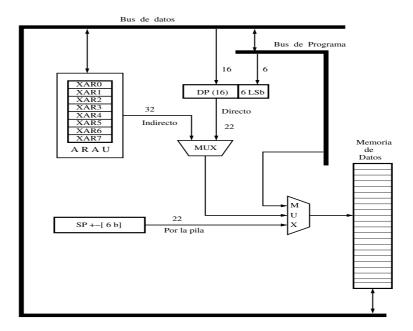

|    |      | 4.2.3. Modo de direccionamiento por la pila                               | 38              |

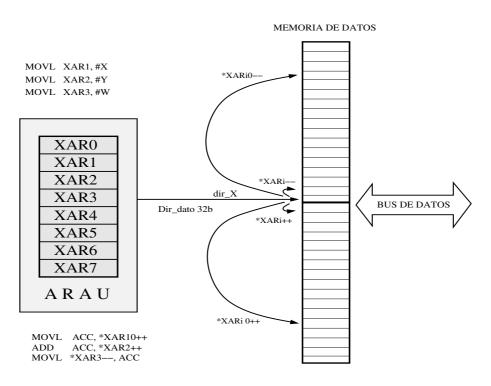

|    |      | 4.2.4. Modo de direccionamiento indirecto                                 | 38              |

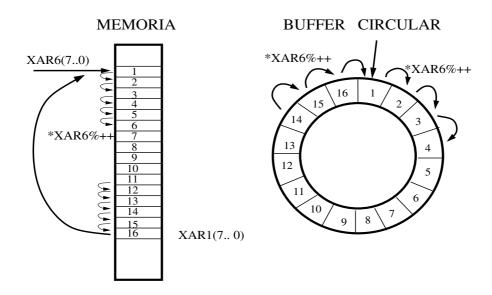

|    |      | 4.2.5. Direccionamiento circular                                          | 43              |

|    |      | 4.2.6. Direccionamiento de registros                                      | 45              |

|    |      | 4.2.7. Modo de direccionamiento al espacio de dato, de programa y espacio |                 |

|    |      | I/O                                                                       | 46              |

|    |      | 4.2.8. Modo de direccionamiento byte                       | 47         |

|----|------|------------------------------------------------------------|------------|

| 5. | Uni  | dad de control                                             | 19         |

|    | 5.1. | Registros de control                                       | 49         |

|    |      |                                                            | 49         |

|    |      |                                                            | 49         |

|    | 5.2. |                                                            | 50         |

|    |      |                                                            | 50         |

|    |      |                                                            | 51         |

|    |      |                                                            | 51         |

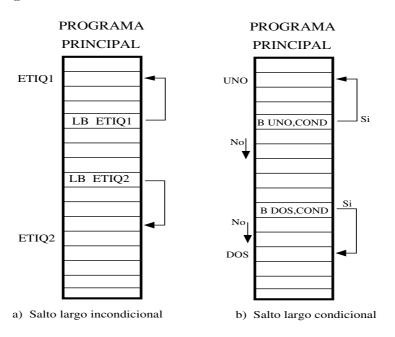

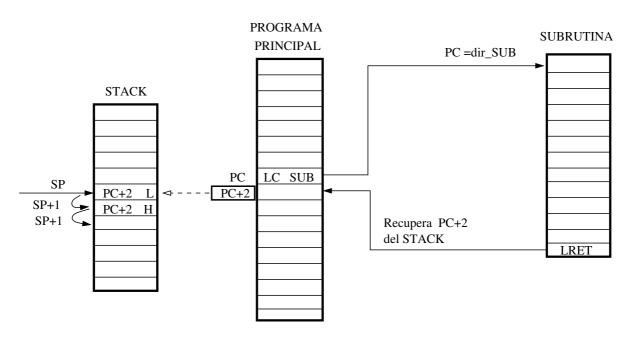

|    |      | 5.2.4. Instrucciones de llamada a subrutina                | 54         |

|    |      | 5.2.5. Llamadas incondicionales a subrutina                | 54         |

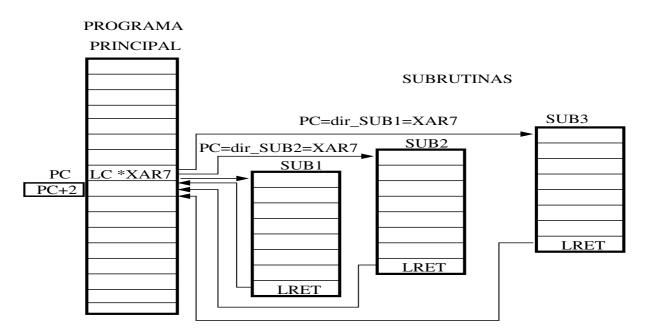

|    |      | 5.2.6. Llamadas dinámicas a subrutina                      | 55         |

|    |      | 5.2.7. Retorno de subrutinas                               | 55         |

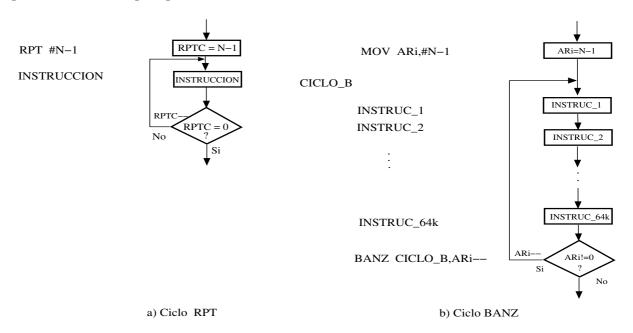

|    |      |                                                            | 55         |

|    | 5.3. |                                                            | 58         |

|    | 5.4. |                                                            | 61         |

|    | 5.5. | Instrucciones                                              | 61         |

|    | 5.6. | Ejemplos en lenguaje ensamblador                           | 35         |

|    |      | 5.6.1. Suma varias constantes en modo inmediato            | 65         |

|    |      | 5.6.2. Suma varios datos en modo directo                   | 66         |

|    |      | 5.6.3. Suma varios datos en modo indirecto                 | 67         |

|    |      | 5.6.4. Decimación de una secuencia                         | <b>6</b> 9 |

|    |      | 5.6.5. Modo de direccionamiento de buffer circular         | 70         |

|    |      | 5.6.6. Producto punto entre dos vectores                   | 70         |

|    |      | ·                                                          | 74         |

|    |      | 5.6.8. Operación a 32 bits                                 | 75         |

|    |      | 5.6.9. Aplicaciones propuestas                             | 77         |

| 6. | Imp  | lementación de filtros digitales                           | 79         |

|    | 6.1. | Filtros de respuesta finita al impulso                     | 79         |

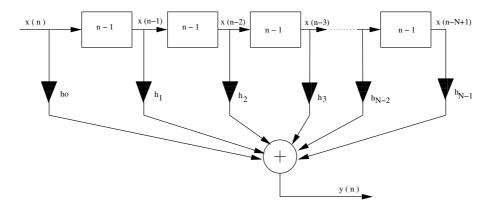

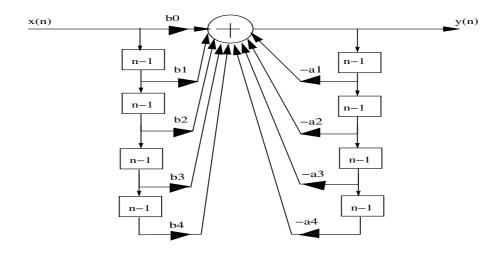

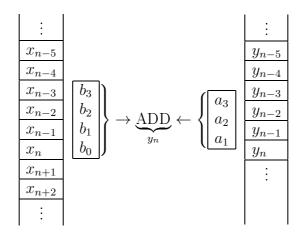

|    |      | 6.1.1. Estructuras de los filtros FIR                      | 79         |

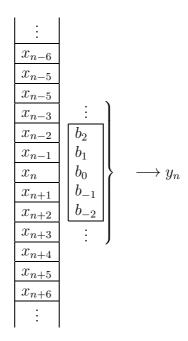

|    |      | 6.1.2. Implementación de líneas de retardo o buffer lineal | 32         |

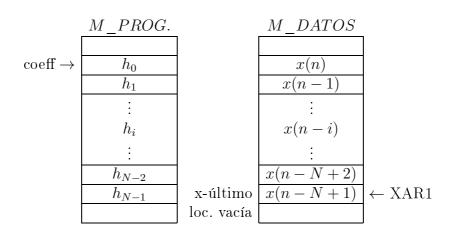

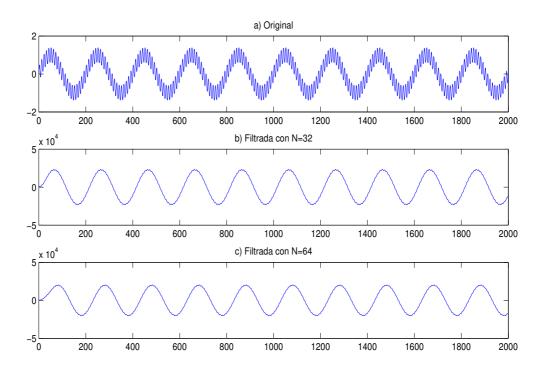

|    |      | 6.1.3. Implementación de filtros FIR                       | 33         |

|    | 6.2. | Filtros de respuesta infinita al impulso                   | 39         |

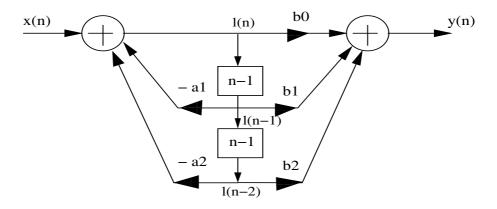

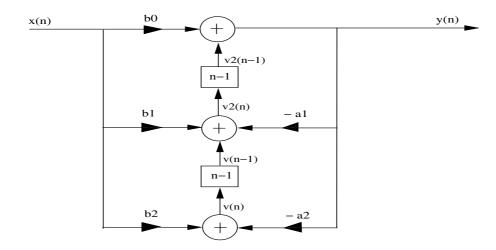

|    |      | 6.2.1. Estructuras de filtros digitales IIR                | 39         |

|    |      | 6.2.2. Filtro IIR forma directa                            | 90         |

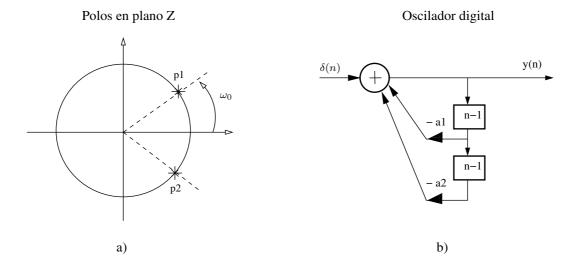

|    | 6.3. | Osciladores digitales                                      | 94         |

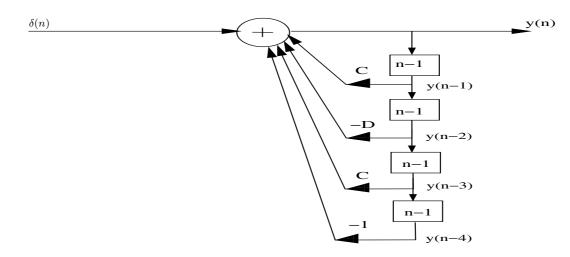

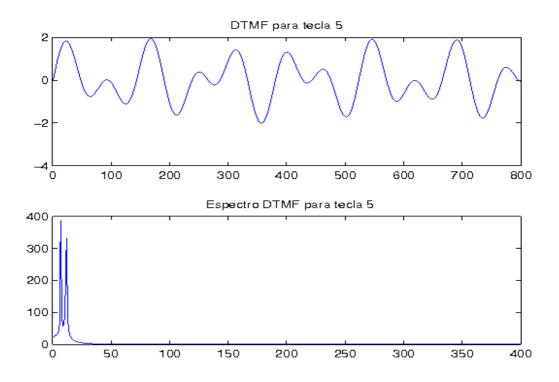

|    | 6.4. | Generación de señales DTMF                                 | 97         |

|    | 6.5. | Aplicaciones propuestas                                    | )3         |

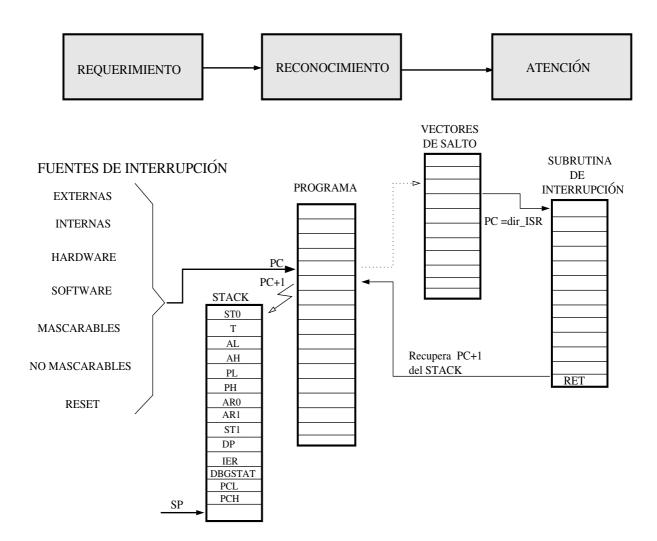

| 7.   | Inte | errupciones 1                                                 | 05  |

|------|------|---------------------------------------------------------------|-----|

| 7.1. |      | Interrupciones del C28x                                       | 105 |

|      |      | 7.1.1. Operación y manejo de interrupciones                   | 106 |

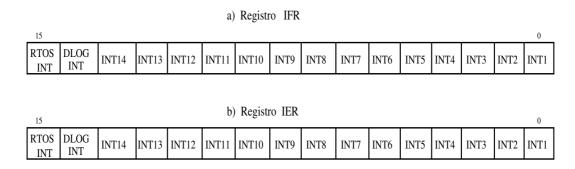

|      |      | 7.1.2. Interrupciones mascarables                             | 109 |

|      |      | 7.1.3. Proceso de atención de interrupciones mascarables      | 110 |

|      |      | 7.1.4. Interrupciones no mascarables                          | 111 |

|      |      | 7.1.5. Interrupciones por software                            | 111 |

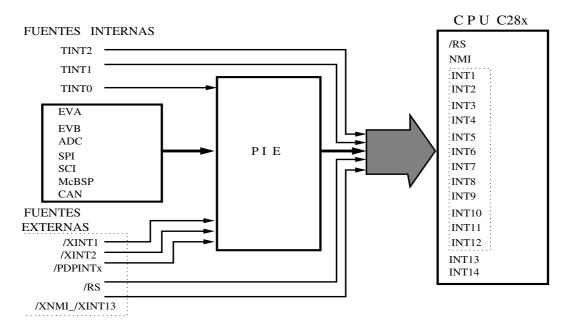

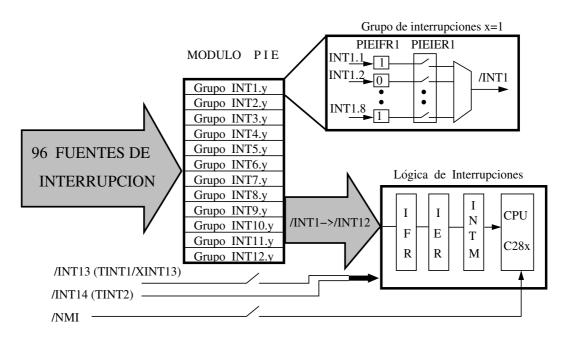

|      | 7.2. | Módulo de expansión de interrupción de periféricos (PIE)      | 113 |

|      |      | 7.2.1. El watchdog o perro guardián                           | 120 |

| 8.   | Peri | iféricos 1                                                    | 23  |

|      | 8.1. | Periféricos de las familias C28xxx                            | 123 |

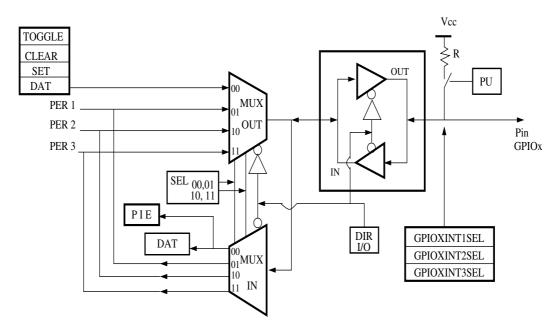

|      | 8.2. | Entradas y salidas de propósito general                       | 124 |

|      |      | 8.2.1. Registros de configuración de GPIO                     | 124 |

|      |      |                                                               | 124 |

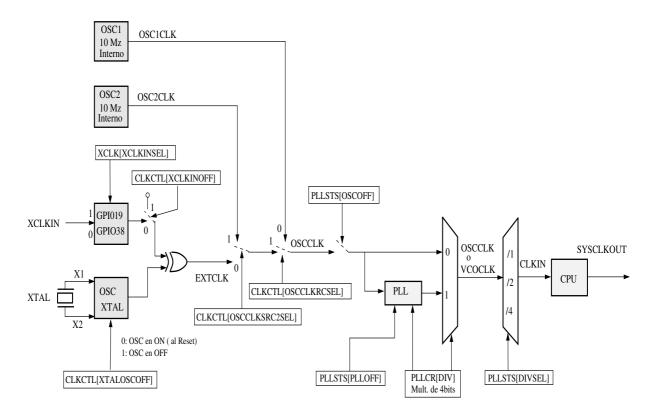

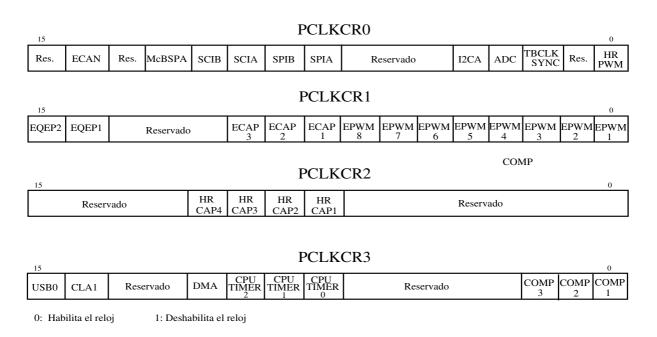

|      | 8.3. | Sistema de reloj                                              | 132 |

|      |      |                                                               | 133 |

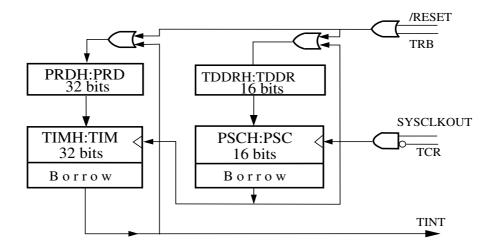

|      | 8.4. |                                                               | 135 |

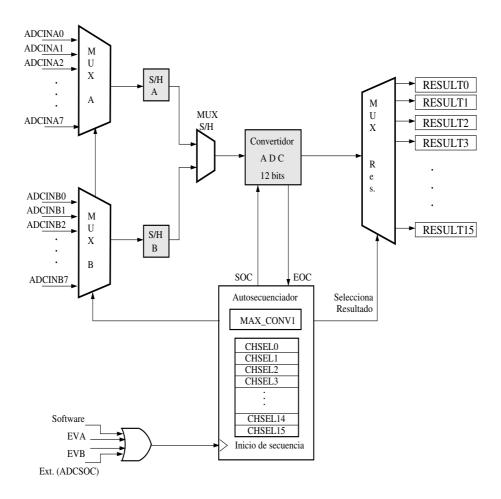

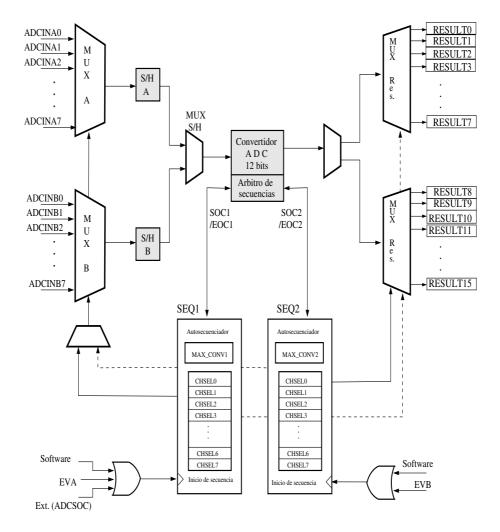

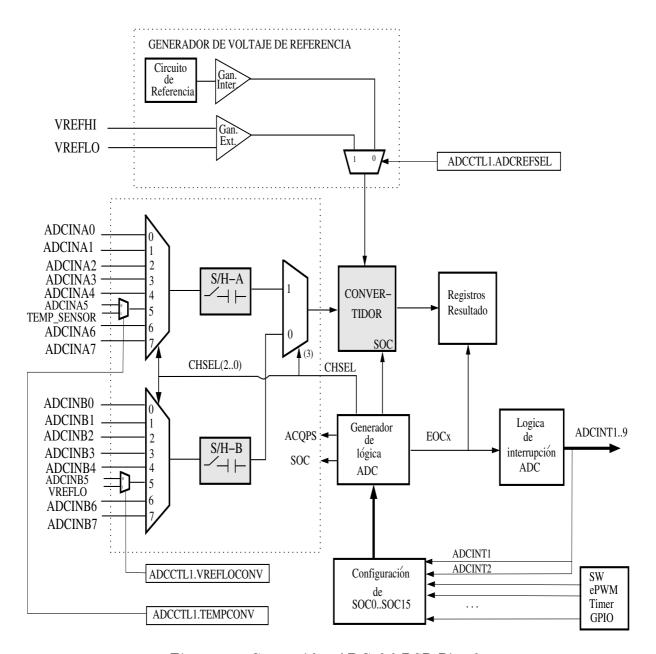

|      | 8.5. | Convertidor análogo digital (ADC)                             | 146 |

|      |      |                                                               | 148 |

|      |      | 8.5.2. Inicialización de registros                            | 149 |

|      | 8.6. |                                                               | 151 |

|      |      | 8.6.1. Principio de operación                                 | 153 |

|      |      | 8.6.2. Configuración                                          | 153 |

|      |      |                                                               | 154 |

|      |      |                                                               | 154 |

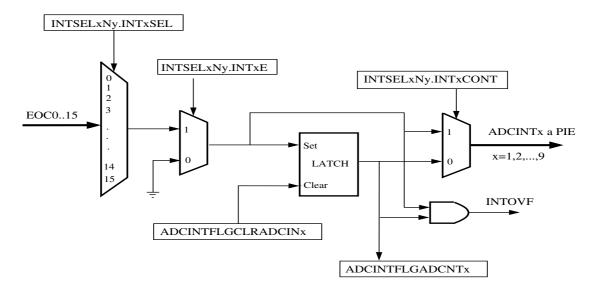

|      |      | 8.6.5. Operación de interrupción y EOC                        | 154 |

|      |      | 8.6.6. Secuencia de encendido de ADC                          | 155 |

|      |      | 8.6.7. Voltajes convertidos con referencias interna y externa | 155 |

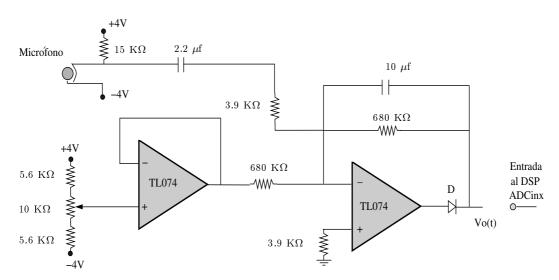

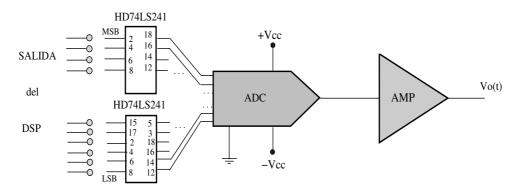

|      |      | 8.6.8. Circuitos electrónicos externos para el ADC y DAC      | 156 |

|      | 8.7. | Aplicaciones propuestas                                       | 163 |

|      | 8.8. | Módulos manejadores de eventos                                | 163 |

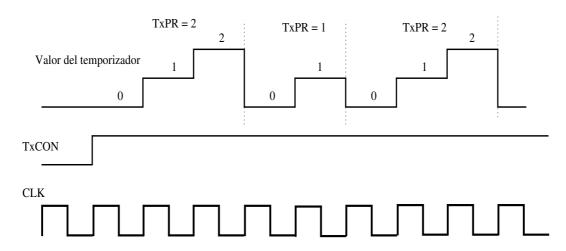

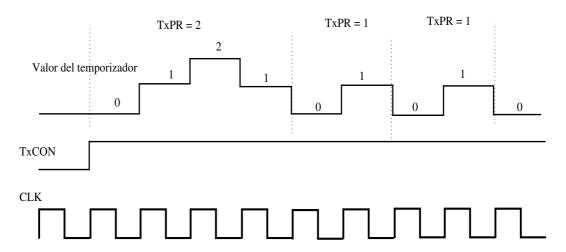

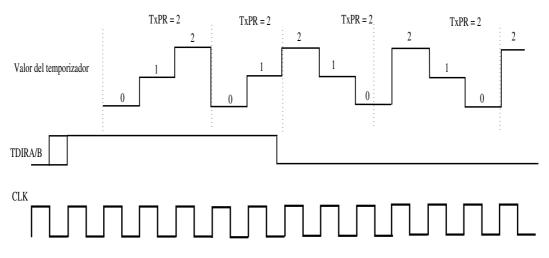

|      |      | 8.8.1. Temporizadores de propósito general para el módulo EV  | 165 |

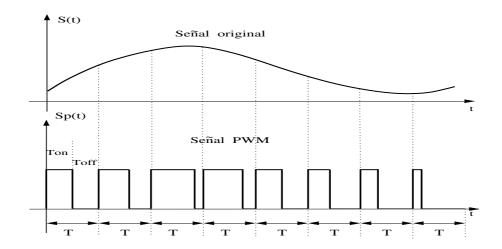

|      | 8.9. | Señales moduladas por ancho de pulso                          | 169 |

|      |      | 8.9.1. Generador de señales PWM                               | 170 |

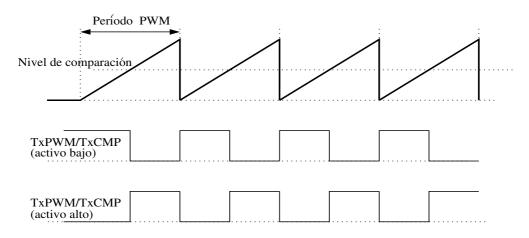

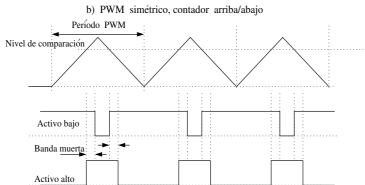

|      |      | 8.9.2. Generador simétrico y asimétrico de PWM                | 171 |

|      |      | 8.9.3. Unidad de captura                                      | 174 |

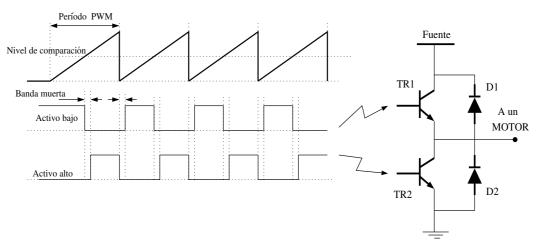

|      |      | 8.9.4. Generador programable de banda muerta "dead band"      | 176 |

|      |      |                                                               | 178 |

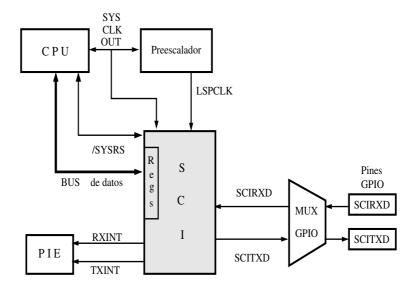

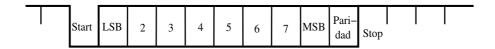

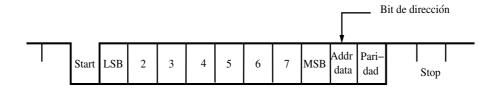

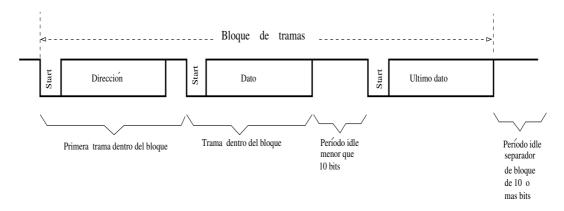

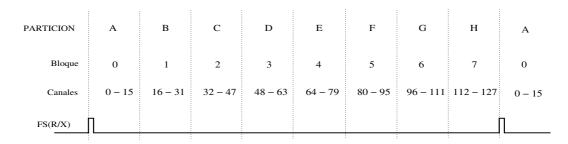

| 9.1. Interfaz de comunicación serial 9.1.1. Características 9.1.2. Comunicación por la interfaz SCI 9.1.3. Interrupción a la interfaz SCI 9.1.4. Comunicación multiprocesos por SCI 9.2. Interfaz de puerto serie (SPI) 9.2.1. Registros de SPI 9.2.2. Operación de la interfaz SPI 9.2.3. Interrupciones de SPI 9.3. Controlador de red de área 9.3.1. Médulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador I2C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal  11. Transferencia por DMA 11.1. Generalidades de operación del DMA 11.2. Ejemplos de aplicación de DMA | 183 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.1.2. Comunicación por la interfaz SCI 9.1.3. Interrupción a la interfaz SCI 9.1.4. Comunicación multiprocesos por SCI 9.2. Interfaz de puerto serie (SPI) 9.2.1. Registros de SPI 9.2.2. Operación de la interfaz SPI 9.2.3. Interrupciones de SPI 9.3. Controlador de red de área 9.3.1. Módulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador I2C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal  11. Transferencia por DMA 11.1. Generalidades de operación del DMA                                                                                                                                            | 183 |

| 9.1.3. Interrupción a la interfaz SCI 9.1.4. Comunicación multiprocesos por SCI 9.2. Interfaz de puerto serie (SPI) 9.2.1. Registros de SPI 9.2.2. Operación de la interfaz SPI 9.2.3. Interrupciones de SPI 9.3. Controlador de red de área 9.3.1. Módulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador I2C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal  11. Transferencia por DMA 11.1. Generalidades de operación del DMA                                                                                                                       | 184 |

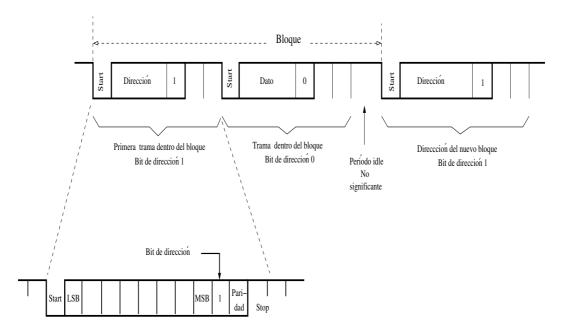

| 9.1.4. Comunicación multiprocesos por SCI  9.2. Interfaz de puerto serie (SPI)  9.2.1. Registros de SPI  9.2.2. Operación de la interfaz SPI  9.2.3. Interrupciones de SPI  9.3. Controlador de red de área  9.3.1. Módulo eCAN  9.3.2. Funcionamiento del controlador eCAN  9.4. Controlador I2C  9.4.1. Funcionamiento  9.4.2. Condiciones START y STOP  9.4.3. Transmisión en formato libre  9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado  10.1. Generalidades  10.2. Compresión logarítmica  10.3. Proceso de recepción de un puerto serie síncrono convencional  10.3.1. Transmisión  10.4. Puerto serie multiplexado por división de tiempo (TDM)  10.6. Puerto serie multicanal buffereado (McBSP)  10.6.1. Registros  10.6.2. Configuración de puertos McBSP  10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF  10.6.4. Registros generadores de razón de muestreo SRGR(1,2)  10.6.5. Operación multicanal  11. Transferencia por DMA  11.1. Generalidades de operación del DMA                                                                                                                                                                                                  | 185 |

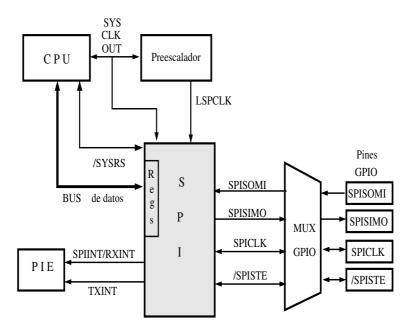

| 9.2. Interfaz de puerto serie (SPI) 9.2.1. Registros de SPI 9.2.2. Operación de la interfaz SPI 9.2.3. Interrupciones de SPI 9.3. Controlador de red de área 9.3.1. Módulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador 12C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal                                                                                                                                                                                                                                                                                                          | 188 |

| 9.2. Interfaz de puerto serie (SPI) 9.2.1. Registros de SPI 9.2.2. Operación de la interfaz SPI 9.2.3. Interrupciones de SPI 9.3. Controlador de red de área 9.3.1. Módulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador 12C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal                                                                                                                                                                                                                                                                                                          | 189 |

| 9.2.2. Operación de la interfaz SPI 9.2.3. Interrupciones de SPI. 9.3. Controlador de red de área 9.3.1. Módulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador I2C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal  11. Transferencia por DMA 11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                               |     |

| 9.2.3. Interrupciones de SPI  9.3. Controlador de red de área  9.3.1. Módulo eCAN  9.3.2. Funcionamiento del controlador eCAN  9.4. Controlador I2C  9.4.1. Funcionamiento  9.4.2. Condiciones START y STOP  9.4.3. Transmisión en formato libre  9.4.4. Requerimiento de interrupciones  10.1. Generalidades  10.2. Compresión logarítmica  10.3. Proceso de recepción de un puerto serie síncrono convencional  10.3.1. Transmisión  10.4. Puerto serie multiplexado por división de tiempo (TDM)  10.6. Puerto serie multicanal buffereado (McBSP)  10.6.1. Registros  10.6.2. Configuración de puertos McBSP  10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF  10.6.4. Registros generadores de razón de muestreo SRGR(1,2)  10.6.5. Operación multicanal  11.Transferencia por DMA  11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                         | 192 |

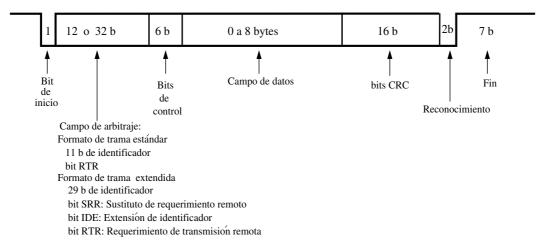

| 9.3. Controlador de red de área 9.3.1. Módulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador I2C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 9.3. Controlador de red de área 9.3.1. Módulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador I2C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal                                                                                                                                                                                                                                                                                                                                                                                                                                       | 196 |

| 9.3.1. Módulo eCAN 9.3.2. Funcionamiento del controlador eCAN 9.4. Controlador I2C 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 9.3.2. Funcionamiento del controlador eCAN  9.4. Controlador I2C  9.4.1. Funcionamiento  9.4.2. Condiciones START y STOP  9.4.3. Transmisión en formato libre  9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado  10.1. Generalidades  10.2. Compresión logarítmica  10.3. Proceso de recepción de un puerto serie síncrono convencional  10.3.1. Transmisión  10.4. Puerto serie buffereado  10.5. Puerto serie multiplexado por división de tiempo (TDM)  10.6. Puerto serie multicanal buffereado (McBSP)  10.6.1. Registros  10.6.2. Configuración de puertos McBSP  10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF  10.6.4. Registros generadores de razón de muestreo SRGR(1,2)  10.6.5. Operación multicanal  11.Transferencia por DMA  11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                     |     |

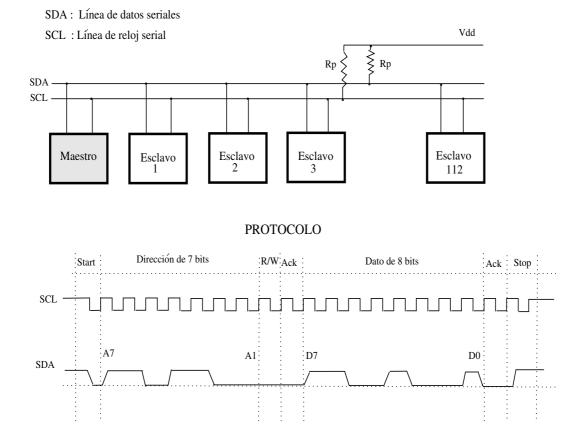

| 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal  11.Transferencia por DMA 11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 9.4.1. Funcionamiento 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal  11.Transferencia por DMA 11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 203 |

| 9.4.2. Condiciones START y STOP 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal  11.Transferencia por DMA 11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 9.4.3. Transmisión en formato libre 9.4.4. Requerimiento de interrupciones  10. Puerto serie multicanal buffereado 10.1. Generalidades 10.2. Compresión logarítmica 10.3. Proceso de recepción de un puerto serie síncrono convencional 10.3.1. Transmisión 10.4. Puerto serie buffereado 10.5. Puerto serie multiplexado por división de tiempo (TDM) 10.6. Puerto serie multicanal buffereado (McBSP) 10.6.1. Registros 10.6.2. Configuración de puertos McBSP 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal  11.Transferencia por DMA 11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 206 |

| 9.4.4. Requerimiento de interrupciones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

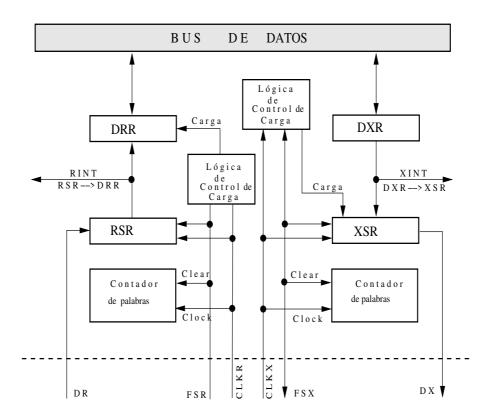

| 10. Puerto serie multicanal buffereado  10.1. Generalidades                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 10.1. Generalidades  10.2. Compresión logarítmica  10.3. Proceso de recepción de un puerto serie síncrono convencional  10.3.1. Transmisión  10.4. Puerto serie buffereado  10.5. Puerto serie multiplexado por división de tiempo (TDM)  10.6. Puerto serie multicanal buffereado (McBSP)  10.6.1. Registros  10.6.2. Configuración de puertos McBSP  10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF  10.6.4. Registros generadores de razón de muestreo SRGR(1,2)  10.6.5. Operación multicanal  11. Transferencia por DMA  11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 10.2. Compresión logarítmica  10.3. Proceso de recepción de un puerto serie síncrono convencional  10.3.1. Transmisión  10.4. Puerto serie buffereado  10.5. Puerto serie multiplexado por división de tiempo (TDM)  10.6. Puerto serie multicanal buffereado (McBSP)  10.6.1. Registros  10.6.2. Configuración de puertos McBSP  10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF  10.6.4. Registros generadores de razón de muestreo SRGR(1,2)  10.6.5. Operación multicanal  11.Transferencia por DMA  11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 209 |

| 10.3. Proceso de recepción de un puerto serie síncrono convencional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 10.3.1. Transmisión  10.4. Puerto serie buffereado  10.5. Puerto serie multiplexado por división de tiempo (TDM)  10.6. Puerto serie multicanal buffereado (McBSP)  10.6.1. Registros  10.6.2. Configuración de puertos McBSP  10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF  10.6.4. Registros generadores de razón de muestreo SRGR(1,2)  10.6.5. Operación multicanal  11.Transferencia por DMA  11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 10.4. Puerto serie buffereado  10.5. Puerto serie multiplexado por división de tiempo (TDM)  10.6. Puerto serie multicanal buffereado (McBSP)  10.6.1. Registros  10.6.2. Configuración de puertos McBSP  10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF  10.6.4. Registros generadores de razón de muestreo SRGR(1,2)  10.6.5. Operación multicanal  11.Transferencia por DMA  11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

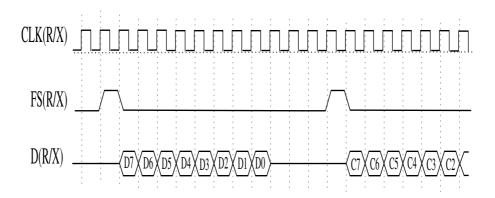

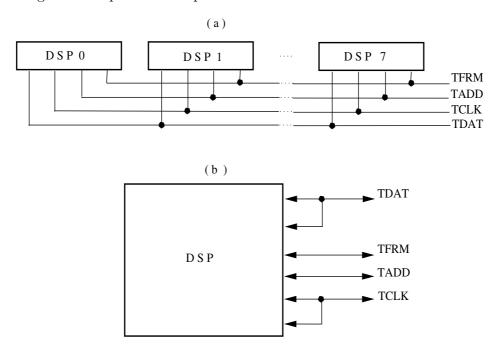

| 10.5. Puerto serie multiplexado por división de tiempo (TDM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

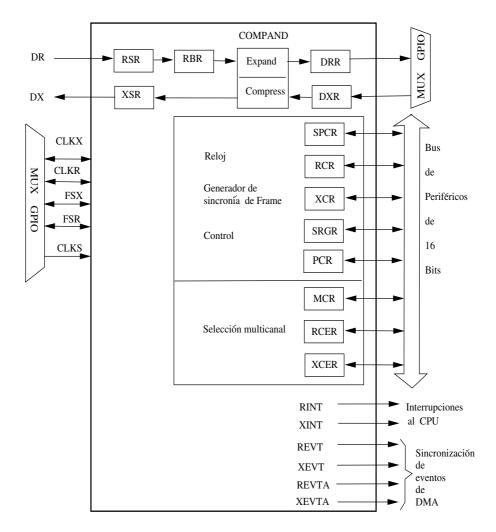

| 10.6. Puerto serie multicanal buffereado (McBSP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 10.6.1. Registros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 10.6.2. Configuración de puertos McBSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 10.6.3. Registros de control de transmisión y recepción RCR(1,2) y XCF 10.6.4. Registros generadores de razón de muestreo SRGR(1,2) 10.6.5. Operación multicanal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

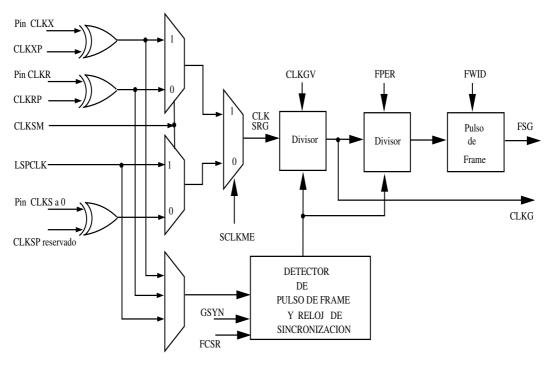

| 10.6.4. Registros generadores de razón de muestreo SRGR(1,2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

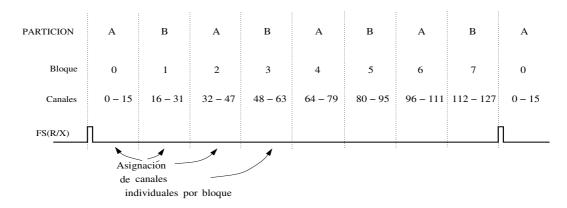

| 10.6.5. Operación multicanal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ` ' |

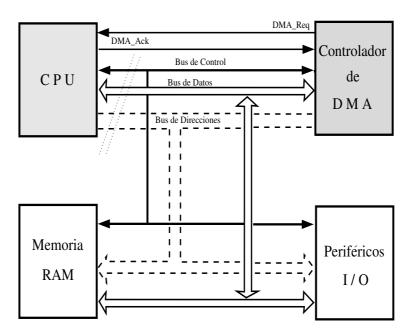

| 11.Transferencia por DMA<br>11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

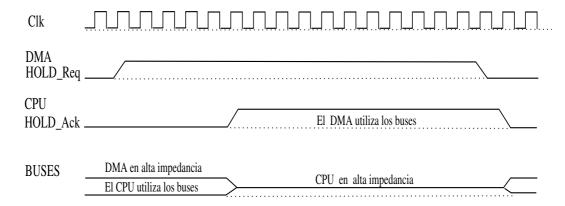

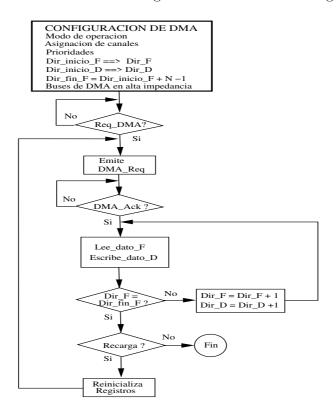

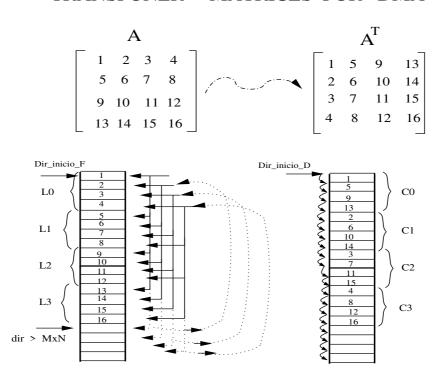

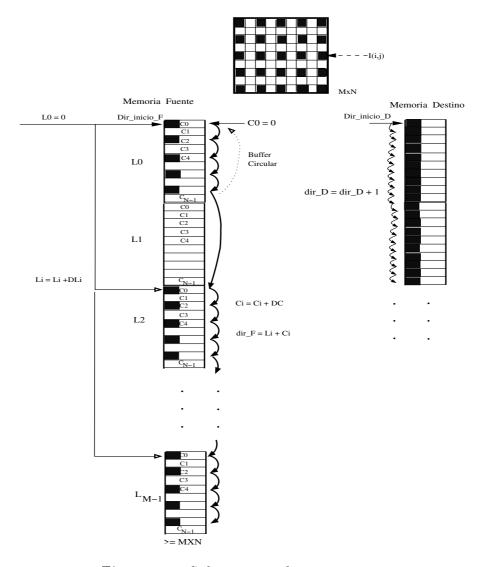

| 11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 229 |

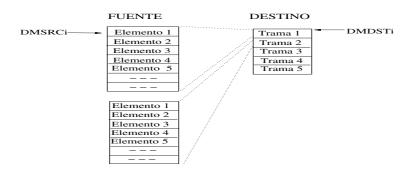

| 11.1. Generalidades de operación del DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 237 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 11.3. Módulo DMA del DSP C28x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 11.3.1. Descripción de registros de DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 11.3.2. Modos de transferencia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 11.3.3. Tabla de registros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| A. Fo | ormatos numéricos                                            | 251 |

|-------|--------------------------------------------------------------|-----|

| A     | .1. Errores numéricos                                        | 251 |

| A     | .2. Formatos de punto fijo                                   | 252 |

|       | A.2.1. Representación de números fraccionarios en punto fijo | 253 |

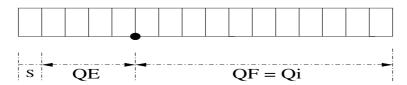

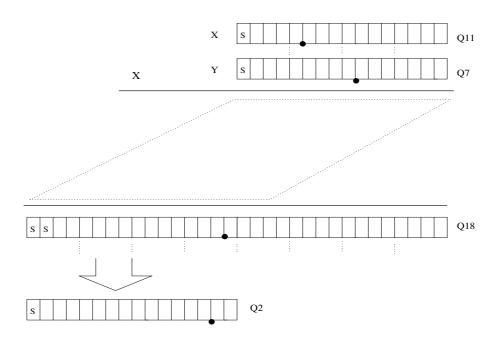

|       | A.2.2. Formatos numéricos de punto fijo $Qi$                 | 254 |

|       | A.2.3. Intervalos dinámicos y precisión numérica             | 256 |

|       | A.2.4. Asignación de variables                               | 258 |

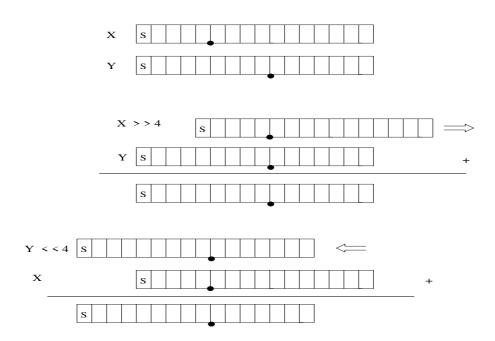

|       | A.2.5. Operación suma en punto fijo                          | 259 |

|       | A.2.6. Operación de multiplicación en punto fijo             |     |

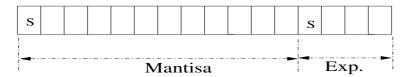

| A     | .3. Formato numérico de punto flotante                       | 262 |

|       | A.3.1. Suma de punto flotante                                | 264 |

|       | A.3.2. Multiplicación de punto flotante                      |     |

|       | A.3.3. División de punto flotante                            | 265 |

| A     | .4. Formatos estándares de punto flotante                    | 265 |

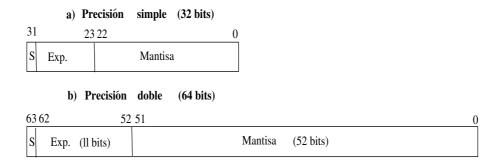

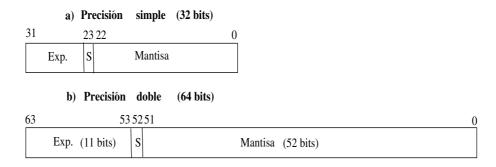

|       | A.4.1. Formato de punto flotante estándar IEEE 754           | 265 |

| A     | .5. Formato de punto flotante de Microsoft                   | 268 |

| A     | .6. Otros formatos                                           | 268 |

| в. с  | Glosario                                                     | 271 |

| Bibli | ografía                                                      | 276 |

| Índice | general |

|--------|---------|

|        |         |

# Capítulo 1

# Introducción

En la actualidad, las aplicaciones del procesamiento digital de señales (PDS) han ido avanzando a pasos agigantados y las podemos encontrar vinculadas a una gran cantidad de actividades de la vida moderna. Entre algunas están: las aplicaciones multimedia, computadoras personales, teléfonos celulares, comunicaciones vía internet, aplicaciones telefónicas, aplicaciones biomédicas, instrumentación, tabletas digitales, video juegos, televisión digital, etc. Por estas razones, un ingeniero que se dedique al área del PDS debe estar en constante actualización en algoritmos, nuevas tecnologías, aplicaciones, nuevos productos, entre otros.

El objetivo de este libro es de carácter académico ya que fomenta el aprendizaje de las familias de procesadores de señales digitales (DSP) TMS320C28xxx, con el fin de que los estudiantes de licenciatura y posgrado adquieran un conocimiento más rápido de estas arquitecturas y puedan en un futuro cercano desarrollar proyectos y aplicaciones en esta área.

Todo el material incluido en este trabajo es la recopilación, condensación, análisis y estructuración de la información de estos DSP que se puede encontrar en más de 30 manuales de Texas Instruments $^{TM}$  (TI), algunos libros y artículos citados en la bibliografía, así como las metodologías empleadas por el autor en su labor académica.

La compañía TI, diseñadora y productora de circuitos integrados, se ha convertido en una empresa líder en la fabricación de DSP y aplicaciones en tiempo real. Esta compañía clasifica sus dispositivos en una serie de grupos denominados familias, cada una de ellas posee diferentes particularidades que los caracteriza. En las últimas décadas, TI ha ido orientando las familias de sus arquitecturas a tres grandes campos de aplicación de ingeniería, las cuales son:

- Control e instrumentación: familias TMS320C2xx, TMS320C28xxx y TMS320F28xxx de punto entero y algunas de punto flotante.

- Comunicaciones, entretenimiento y aplicaciones de bajo consumo: familias TMS320C5x, TMS320C54xx y TMS320C55xx de punto entero.

■ Alto desempeño y video: familias TMS320C64xx de punto entero y TMS320C67xx de punto flotante.

La familia TMS320C28x (C28x) con tecnología CMOS y TMS320F28x (F28x) con memoria flash que se aborda en este trabajo, contiene una arquitectura interna de un procesador digital que integra un gran número de periféricos y memoria, es decir, que conjunta la potencialidad de un DSP con las prestaciones de un microcontrolador. Estas características lo convierten en una plataforma de alto desempeño en el diseño de aplicaciones de control de motores, instrumentación, soluciones embebidas en un sólo chip, manejo de potencia, comunicaciones y procesamiento digital de señales.

Los DSP C28x y F28x (genéricamente los llamaremos C28x) son arquitecturas de aritmética de 16 y 32 bits en punto entero y algunas de punto flotante, diseñados especialmente para aplicaciones de control de alto desempeño; tales como robótica, automatización industrial, dispositivos de almacenamiento masivo, control de iluminación, instrumentación, fuentes de potencia y otras aplicaciones que necesitan de un procesador simple que resuelva problemas complejos.

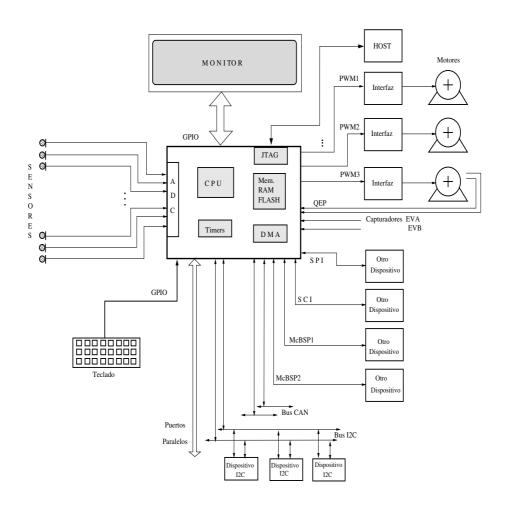

En la figura 1.1 se muestra un sistema embebido que integra un conjunto de periféricos externos, adquisición de varias señales, comunicaciones con periféricos y otros dispositivos, salidas, control de procesos, control de motores, etc., que son manejados por un sistema central en tiempo real, un dispositivo capaz de realizar todas estas acciones puede ser un DSP C28x. En la actualidad se requieren soluciones de esta naturaleza que involucre una gran cantidad de opciones en un sólo sistema, la figura 1.1 nos da una idea de la potencialidad del dispositivo a tratar.

Este trabajo no sólo se enfoca al estudio del hardware de las arquitecturas C28x, sino que considera aspectos teóricos del PDS donde se enfatiza la importancia de los DSP, además, se presentan muchos ejemplos para abundar en el software. Los ejemplos están elaborados en lenguaje ensamblador para profundizar en el manejo del hardware; sin embargo, estos dispositivos permiten programarse en lenguaje C y C++. El autor considera que cuando un diseñador tiene un conocimiento profundo del hardware, la migración a la programación de los DSP en lenguaje C es más fácil, por tanto se pueden optimizar las aplicaciones utilizando lenguaje ensamblador, lenguaje C o combinando ambos.

Los DSP de la familia C5x son dispositivos con aritmética de punto entero a 16 bits cuya versión más rápida alcanzó los 80 millones de instrucciones por segundo (MIPS), los DSP C54xx también son de punto fijo a 16 bits con bajo consumo de potencia con un desempeño de hasta 200 MIPS, mientras que el C6416 es un DSP tipo RISC con diseño tipo VLWI (very large word instruction), con aritmética de punto fijo a 32 bits que en la actualidad alcanzan desempeños mayores a los 8,000 MIPS. Además, TI también ha desarrollado arquitecturas llamadas plataformas abiertas para multimedia (OMAP) que integran DSP de la familia C55xx con arquitecturas ARM (Advanced RISC Machine), OMAP con TMS320C6748 y ARM, y arquitecturas muy específicas para video llamadas Davinci como el TMS320DM6467 que constan de un TMS320C6416 con un coprocesador de video integrado.

Figura 1.1. Sistema embebido utilizando un DSP C28x

#### Resumen de capítulos:

En el capítulo dos, se exponen las características generales más importantes de las familias C28x y F28x, partiendo desde las familias básicas hasta las de punto flotante. En el capítulo tres, se explican los bloques principales de la arquitectura del C28x, con el fin de ir conociendo sus partes y luego en los siguientes capítulos hacer uso de éstos. En el capítulo cuatro, nos adentramos en el conocimiento de la memoria, sus bloques principales y los modos de direccionamiento que se utilizan para la transferencia de datos en la arquitectura. Se presentan ejemplos en lenguaje ensamblador. En el capítulo cinco, el control de la máquina, se estudian los registros de control y estado, se muestran las instrucciones relacionadas con el cambio de flujo de un programa y se estructuran ejemplos de aplicaciones. En el capítulo seis, se presenta una breve introducción a los filtros digitales con varios ejemplos. En el capítulo siete, se analiza la forma de interactuar del CPU a través de interrupciones y se estudia la interfaz de expansión de interrupciones. En el capítulo ocho, se introduce a los periféricos y su interfaz con que interactúa el DSP. En el capítulo nueve, se presentan los diferentes puertos seriales que contiene esta familia de DSP. En el capítulo diez, el puerto multicanal serial (McBSP), un poderoso puerto serial que opera en varios modos y puede manejar hasta 128 canales de 32 bits en combinación con el DMA. En el capítulo once, la transferencia por acceso directo a memoria (DMA) como una técnica de procesamiento en paralelo muy poderosa en cuanto al manejo de información. Adicionalmente, se agrega un apéndice de formatos numéricos como una parte importante de las aplicaciones del PDS y los DSP, ya que es necesario conocer cómo se manejan los números en forma binaria.

El autor reconoce la valiosa colaboración que ha tenido el programa universitario de Texas Instruments en la donación de tarjetas al Laboratorio de Procesamiento Digital de Señales, esto ha contribuido a la enseñanza y aprendizaje de los DSP en la Facultad. También agradece a la Unidad de Apoyo Editorial de la Facultad de Ingeniería por su revisión y apoyo en la publicación de esta obra, así como a los ingenieros Agustín Silva y Samuel Vázquez por sus sugerencias y pruebas realizadas con estos DSP.

Larry Escobar Profesor de la Facultad de Ingeniería, UNAM. Ciudad Universitaria, México D. F., marzo de 2014. e-mail: larryesc@gmail.com

# Capítulo 2

# Características generales de la familia F28xx

Como es sabido por los ingenieros, cuando se realiza un diseño, antes de llevarlo a su implementación es necesario conocer las características de los dispositivos que cumplan con las especificaciones, por tanto, en este capítulo se pretende dar a conocer las características generales de los DSP de la familia TMS320C2xxx C28x que genéricamente se le conoce como C28x, donde la letra C se refiere a la tecnología original CMOS, sin embargo, si hacemos referencia a las familias que contienen memoria flash se les nombra F28x, las familias con cuatro dígitos C28xx o F28xx y con cinco dígitos F28xxx

En este capítulo se abordan las características generales de los DSP familias F28x y F28xxx, se describe la arquitectura, sus rasgos más relevantes como su unidad de proceso, memoria, buses y periféricos. Se resaltan en particular las familias F280x y F281x, porque en este libro se desarrollarán ejemplos y prácticas con los DSP F2808, F2812 y eventualmente con el DSP Piccolo F28027 y F28069.

La generación de DSP C28x son un conjunto de dispositivos de la familia de DSP TMS320C2000 o también llamados controladores de señales digitales (DSC) de Texas Instruments (TI) con arquitectura Harvard modificada [18]. Estos dispositivos son de alta integración para aplicaciones de alto desempeño en control en instrumentación, en general, se puede decir que estas familias están constituidas por un DSP con un microcontrolador con características CISC (conjunto amplio de instrucciones) y ejecutan la mayoría de instrucciones en un ciclo de reloj. La unidad central de proceso (CPU) del C28x es muy eficiente en cuanto al uso de lenguajes como C y C++ que permite desarrollos en aplicaciones matemáticas en el procesamiento digital de señales (PDS), así como aplicaciones típicas de microcontroladores en sistemas de control.

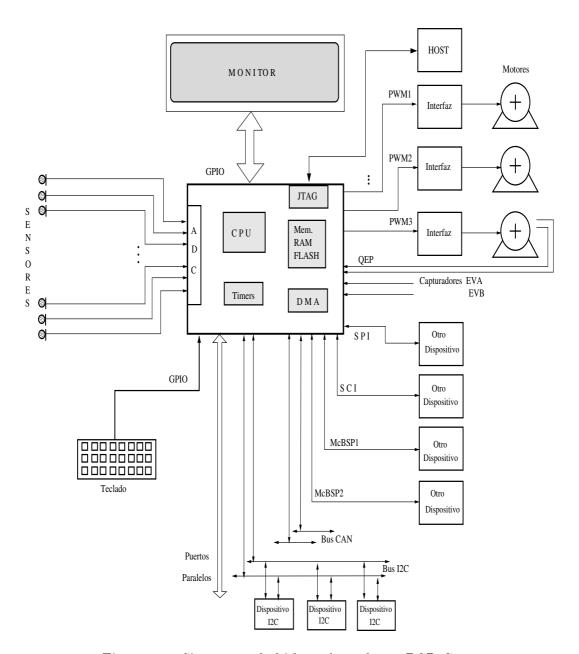

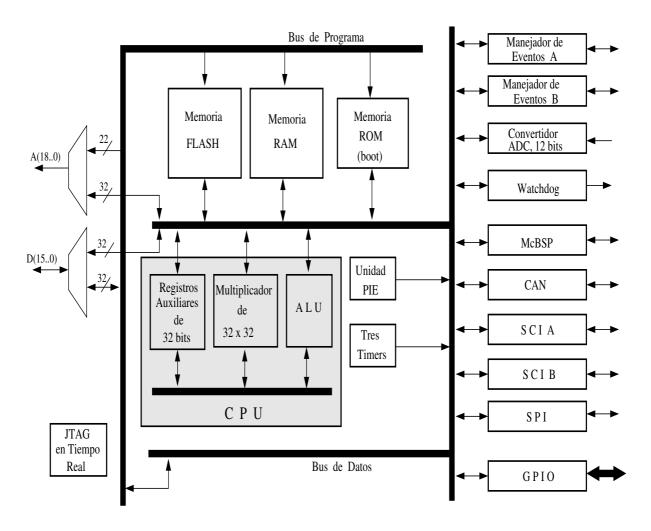

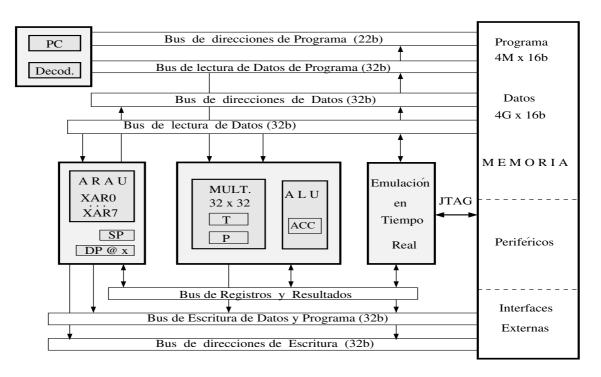

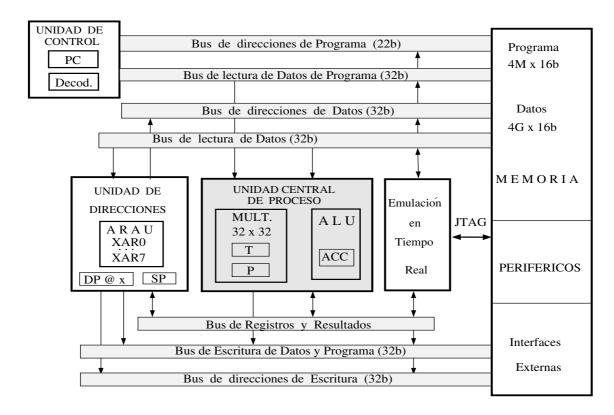

En la figura 2.1 se ilustran los bloques principales de estas arquitecturas, donde podemos observar bloques como la unidad central de proceso CPU, la memoria, buses de datos y de programa, periféricos, un bloque manejador de interrupciones (PIE) y una interfaz de depuración y emulación JTAG (joint test action group) en tiempo real, todas estas partes se

Figura 2.1. Arquitectura general de los DSP C28x

estudiarán en los capítulos siguientes.

La generación TMS320C28x surge como evolución de la familia TMS320C24x de 16 bits, es una versión ampliada, mejorada y compatible con esta familia. Posee un CPU de 32 bits de punto fijo, con una capacidad de hasta los 150 MIPS y voltajes de alimentación de 1.9 V para el CPU y 3.3 V para los periféricos. En versiones avanzadas existen arquitecturas de punto flotante con el estándar 754 de IEEE.

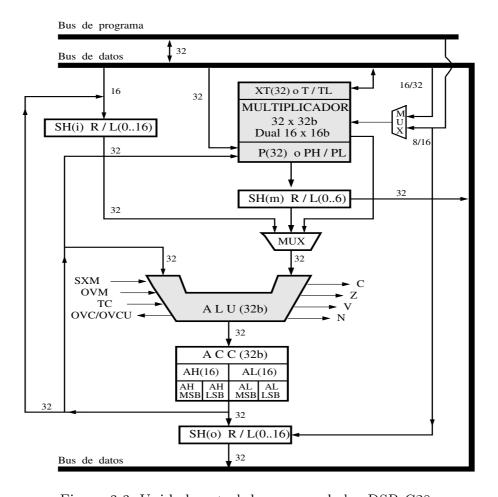

El CPU en sí es un procesador digital de señales de 32 bits para la realización de las operaciones aritméticas y lógicas con características generales:

- Arquitectura tipo Harvard modificada.

- Ejecuta instrucciones de 32 bits para mejorar la precisión numérica.

- Ejecuta instrucciones de 16 bits para mejorar la eficiencia en el código.

- Unidad aritmética lógica (ALU) de 32 bits.

- Unidad aritmética de registros auxiliares (ARAU), genera direcciones de memoria dato, realiza aritmética entre apuntadores en paralelo con operaciones de la ALU.

- Registro de corrimiento, ejecuta corrimientos hacia la derecha o izquierda de hasta 16 bits.

- Ejecuta multiplicaciones de 32 x 32 bits con resultado de 64 bits.

- Efectúa una operación multiplicación acumulación (MAC) de 32 x 32 bits en un ciclo de reloj.

- Efectúa dos operaciones MAC de 16 x 16 bits (DMAC) en un ciclo de reloj.

- Emulación de su funcionamiento en tiempo real.

- Protección de código.

- En un ciclo de instrucción puede ejecutar instrucciones que leen, modifican v escriben en memoria.

- Respuesta de interrupciones rápida con salvado automático del contexto.

- Sincronía de eventos con latencia mínima.

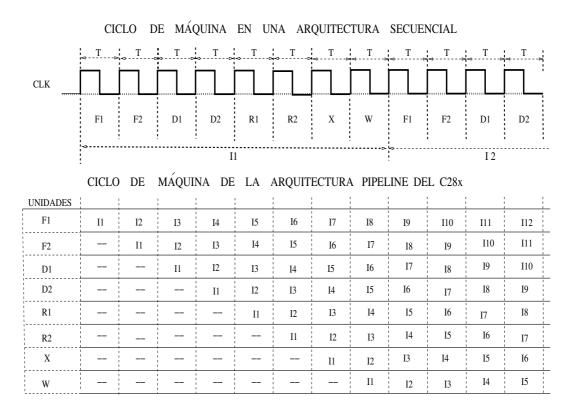

- Pipeline de 8 niveles, que permiten un solapamiento máximo de 8 instrucciones en niveles de ejecución diferentes:

- Búsqueda de instrucción: F1 y F2.

- Decodificación: D1 y D2.

- Lectura de operandos: R1 y R2.

- Ejecución: X.

- Escritura: W.

#### Periféricos:

- 16 convertidores A/D a 12 bits.

- Memoria flash interna.

- Interfaz JTAG estándar IEEE 1194.1 1990 para emulación y depuración en tiempo real.

- Canales para interfaz de comunicación serial (SCI).

- Módulos para interfaz de puerto serial UART (SPI).

- Módulos para comunicación por buses I2C.

- Módulo de control de red de área (CAN), que es un protocolo de comunicación industrial para control distribuido en tiempo real.

- Bloque de expansión de periféricos (PIE).

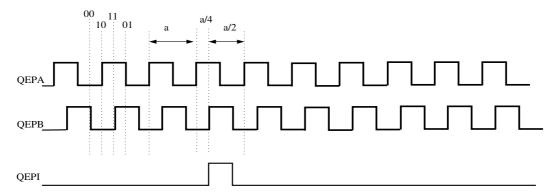

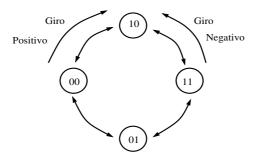

- Módulos de codificación en cuadratura (QEP).

#### Para versiones avanzadas

- Módulo McBSP (multichannel buffered serial port). Es un puerto serie síncrono multicanal que tiene como características principales:

- Hasta 128 canales

- Comunicación full-duplex

- Relojes y tramas independientes programables para transmisión y recepción con dos registros FIFOs de 32 bits y 16 niveles.

- Seis canales de acceso directo a memoria (DMA).

- Unidad aceleradora de punto flotante a 32 bits.

- Unidad de punto flotante (FPU) con precisión simple IEEE-754.

- Unidad de matemáticas complejas y el algoritmo Viterbi (VCU).

#### Familias F2823x y F2833x

Las familias de DSP F28232, F28234, F28235, F28332, F28334 y F28335 están basadas en la arquitectura del DSP C28x, con mejoras que agregan más potencialidad en sus periféricos y diferencias en cuanto al mapa de memoria; la familia F2833x incluye una unidad de punto flotante (FPU) mientras que la familia F2823x sigue operando en punto entero y son familias que agregan transferencia por acceso directo a memoria (DMA).

La familia F2833x es un DSP C28x con una unidad FPU (C28x + FPU), está basada en controladores con arquitectura de punto entero a 32 bits, la unidad FPU efectúa operaciones de punto flotante en precisión simple utilizando el estándar 754 IEEE. Esto permite la implementación eficiente de algoritmos de control y PDS a mayor precisión numérica, prescindiendo de un segundo procesador, estas familias son las más avanzadas de los DSP C28x.

Las arquitecturas F2833x, siguen manteniendo la base de las arquitecturas C28x, pero

aumenta en gran medida su potencialidad, ya que se agrega una unidad de punto flotante (FPU) de 32 bits con el estándar IEEE 754, ocho registros de 32 bits para operaciones de FPU, aumenta la cantidad de memoria flash y memoria OTP, agrega puertos seriales multicanal buffereados y seis canales de DMA entre otros. En la tabla 2.1 se resumen y comparan las características más importantes entre algunas familias C28x.

En la actualidad las familias más avanzadas son la C2834x ejecutan 300 MIPS para punto entero y 600 MFLOPS para punto flotante.

| Característica \ <b>DSP</b> | F2808 | F2812 | F28027 | F28069 | F28235 | F28335 |

|-----------------------------|-------|-------|--------|--------|--------|--------|

| CLK (Mhz)                   | 100   | 150   | 60     | 80     | 150    | 150    |

| RAM (Kw)                    | 18    | 18    | 6      | 50     | 36     | 36     |

| FLASH (Kw)                  | 64    | 128   | 36     | 128    | 256    | 256    |

| PWM                         | 16    | 16    | 9      | 16     | 18     | 18     |

| HRPWM                       | 4     | _     | 4      | 8      | 6      | 6      |

| QEP                         | 2     | 2     | 0      | 2      | 2      | 2      |

| EV                          | 4     | 6     | 1      | 3      | 6      | 6      |

| Timers                      | 14    | 8     | 9      | 16     | 16     | 16     |

| I2C                         | 1     | _     | 1      | 1      | 1      | 1      |

| SCI UART                    | 2     | 2     | 1      | 2      | 3      | 3      |

| SPI                         | 4     | 1     | 1      | 2      | 1      | 1      |

| CAN                         | 2     | 1     | _      | 1      | 2      | 2      |

| GPIO                        | 35    | 56    | 22     | 54     | 88     | 88     |

| McBSP                       | _     | 1     | _      | 1      | 2      | 2      |

| DMA                         | _     | _     | _      | 6      | 6      | 6      |

16

217

3.3

16

180

3.3

16

80

1.9

16

80

1.9

16

160

1.8

16

80

1.9

Tabla 2.1. Comparación de algunos DSP de la familia C28x

## Resumen

Canales ADC

ADC Tc (ns)

Voltaje de CPU

En este capítulo se han presentado las características más sobresalientes de las familias de procesadores C28x, en algunas familias se ha profundizado este aspecto, ya que se pretende que más adelante se realicen ejemplos y prácticas sobre éstas en particular. Se ha introducido un poco a la arquitectura y se irá describiendo y avanzando posteriormente.

| erales de la fan |  |  |  |

|------------------|--|--|--|

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

|                  |  |  |  |

# Capítulo 3

# Arquitectura de la familia F28xx